# Hybrid Transistor for future Power Integrated Circuits

Suseendran GANESSANE

Master of Science Thesis Stockholm, Sweden, 2006

ICT/ECS/ 2006-61

# HYBRID TRANSISTOR FOR FUTURE POWER INTEGRATED CIRCUITS

Master of Science Thesis in "System on Chip Design (SoC Design)"

by

# Suseendran GANESSANE

Stockholm, [06 2006]

# **KTH Supervisor/Examiner:**

# **Dr. Svante Signell**

Royal Institute of Technology (KTH) School of ICT, ECS/ESD Lab Stockholm, Kista, Sweden.

#### **Industrial Supervisor:**

**Dr. Jan Šonský** Senior Scientist PHILIPS Research Leuven Leuven, Belgium.

# ABSTRACT

The future Power Integrated Circuits for power management and automotive electronics will require higher level of integration of power electronic components into advanced CMOS technology processes as compared to today's applications. Current generation of lateral high voltage/power devices cannot be further scaled. Given the ever increasing cost per mm<sup>2</sup> of silicon area in every new CMOS generation, the integration of these traditional HV/power components is fast becoming uneconomical. Their replacement with vertical devices, dominating the discrete component market due their inherently better specific on-resistance, which makes them better suitable for scaling, is not obvious. The processing of vertical devices is either incompatible with planar CMOS manufacturing or the integration of both processes results in unacceptably large degree of complexity prohibiting commercialization.

In this work, a novel hybrid transistor combining advantages of both vertical and lateral (planar) devices is analyzed. Similarly to vertical devices, the hybrid transistor features vertical current flow in both gate channel region and drift (or extended-drain) region allowing very low specific on-resistance and thus very compact size. Simultaneously, all device terminals – Source, Drain, Gate and Field Plate – are placed on the top surface, as it is common for planar devices. This fact combined with simple processing guarantees straightforward integration of hybrid transistor into any CMOS technology. The vertical drift region is accompanied with a field plate, which allows high breakdown voltage and low specific on-resistance.

This device was analyzed using numerical simulations. Potential distribution in the off-state was mainly studied with respect to different device parameters, e.g. trench depth and width, doping concentration and oxide thickness under the field plate. We aimed at maximizing breakdown voltage ( $BV_{DS}$ ) for minimal device size and maximal doping concentration in the drift region. The device construction was optimized for 50 V and 100 V domains.

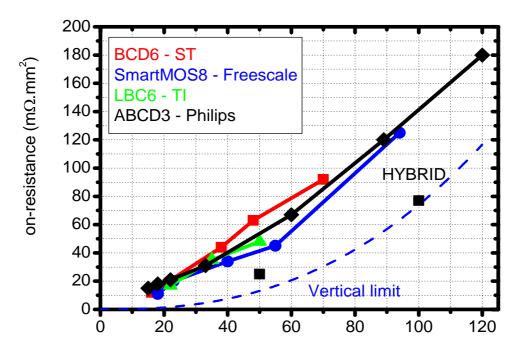

Finally, the on-state regime of the hybrid power transistor was simulated to determine the specific on-resistance ( $R_{on,sp}$ ). A specific on-resistance of 76.7 m $\Omega$ mm<sup>2</sup> for a breakdown voltage of 100 V was determined. This is an excellent  $BV_{DS} - R_{on.sp}$  trade-off outperforming any existing lateral device.

**Key words**: Power Integrated Circuits, Breakdown Voltage, High Voltage, Specific on-resistance, RESURF, Field plate, TrenchMOS, Automotives.

# **ACKNOWLEDGEMENTS**

The work presented in this thesis could not have been done without the aid and support of many people. Therefore I have a great honor to express my sincere gratitude to all.

First of all, I would like to thank **Dr. Rob van Dalen** for offering me such a great opportunity to conduct my Master Thesis at the **Philips Research Leuven**, Belgium and also for introducing me to the very interesting field of device modeling.

Next, I wish to express my special gratitude to the daily advisor/supervisor, **Dr. Jan**  $\check{S}onsk\check{y}$ , who was very kind, encouraging and available whenever needed throughout the thesis work.

I would also like to acknowledge my debt to **Dr. Anco Heringa** for the valuable discussions on the simulation software MEDICI.

I thank all the members of the SPDT/SPO group for the positive research atmosphere and the sharing of interesting ideas and for the indispensable logistic support.

I would like to express my sincere gratitude to **Dr. Svante Signell**, my supervisor/examiner at KTH for accepting me as his master thesis student amidst all his busy schedules and for his valuable guidance throughout my work.

Finally, I am indebted to my parents and my brother for their unconditional support and continuous encouragement throughout my study.

# TABLE OF CONTENTS

| ABSTRACT                                                                                                           | 3  |

|--------------------------------------------------------------------------------------------------------------------|----|

| ACKNOWLEDGEMENTS                                                                                                   | 4  |

| TABLE OF CONTENTS                                                                                                  | 5  |

| LIST OF FIGURES                                                                                                    | 7  |

| LIST OF TABLES                                                                                                     | 8  |

| CHAPTER I INTRODUCTION                                                                                             | 9  |

| 1.1 OVERVIEW OF POWER DEVICES                                                                                      |    |

| 1.2 EXISTING SOLUTIONS                                                                                             |    |

| 1.3 STUDIED DEVICE CONCEPT                                                                                         | 10 |

| 1.4 STRUCTURE OF THE REPORT                                                                                        | 11 |

| CHAPTER II SIMULATION TOOLS                                                                                        | 12 |

| 2.1 INTRODUCTION                                                                                                   | 12 |

| 2.2 MEDICI 2D DEVICE SIMULATION PROGRAM                                                                            | 12 |

| 2.3 SIMULATED CHARACTERISTICS                                                                                      | 12 |

| CHAPTER III PN-JUNCTION DIODE                                                                                      | 14 |

| 3.1 INTRODUCTION                                                                                                   | 14 |

| 3.2 BREAKDOWN VOLTAGE                                                                                              |    |

| 3.3 THE SIMULATED STRUCTURE                                                                                        |    |

| 3.4 SIMULATION AND ANALYSIS                                                                                        |    |

| 3.5 ANALYTICAL VS NUMERICAL RESULTS                                                                                |    |

| CHAPTER IV FIELD-PLATED DIODE                                                                                      |    |

| 4.1 FIELD PLATE AND BREAKDOWN VOLTAGE                                                                              | 22 |

| 4.2 THE SIMULATED STRUCTURE                                                                                        |    |

| 4.3 SIMULATION AND ANALYSIS                                                                                        |    |

| 4.4 NORMAL DIODE VS. FIELD-PLATED DIODE                                                                            |    |

| CHAPTER V HYBRID DIODE                                                                                             | 27 |

| 5.1 Hybrid high voltage device: Introduction                                                                       | 27 |

| 5.2 THE SIMULATED STRUCTURE                                                                                        |    |

| 5.3 SIMULATION AND ANALYSIS                                                                                        | 29 |

| 5.4 Hybrid diode for 50 V domain                                                                                   |    |

| 5.5 Hybrid diode for 100 V domain                                                                                  |    |

| 5.6 CONCLUSION                                                                                                     | 35 |

| CHAPTER VI HYBRID TRANSISTOR                                                                                       | 36 |

| 6.1 INTRODUCTION                                                                                                   | 36 |

| 6.2 THE SIMULATED STRUCTURE                                                                                        |    |

| 6.3 SIMULATION RESULTS AND ANALYSIS                                                                                |    |

| 6.3.1 50V Hybrid transistor: off-state characteristics                                                             |    |

| 6.3.2 50 V Hybrid transistor: on-state characteristics                                                             |    |

| 6.3.3 100V Hybrid transistor: off-state characteristics<br>6.3.4 100 V Hybrid transistor: on-state characteristics |    |

| 6.4 BENCHMARKING                                                                                                   |    |

| VII CONCLUSION                                                                                                     |    |

|                                                                                                                    |    |

| 7.1 PRESENT WORK                                                                                                   |    |

| 7.2 FUTURE WORK                                                                                                    |    |

| LIST OF ABBREVIATIONS                                                                                              |    |

| LIST OF SYMBOLS                                                                                                    | 46 |

| REFERENCES                       |    |

|----------------------------------|----|

| APPENDIX                         |    |

| A.I HYBRID NMOS DEVICE STRUCTURE | 50 |

| A.II SIMULATION DATA             |    |

# **LIST OF FIGURES**

| FIG. 1.1: APPLICATION OF POWER DEVICES IN RELATION TO VOLTAGE AND CURRENT RATINGS                        |    |

|----------------------------------------------------------------------------------------------------------|----|

| FIG. 3.1: P-N JUNCTION DIODE                                                                             |    |

| FIG. 3.2: I-V CHARACTERISTICS OF A P-N JUNCTION DIODE                                                    | 15 |

| FIG. 3.3: P-N JUNCTION DIODE SCHEMATIC                                                                   | 17 |

| FIG. 3.4: DOPING, ELECTRON AND HOLE CONCENTRATION AT ZERO BIAS (LEFT) AND REVERSE                        |    |

| VOLTAGE OF 1V (RIGHT)                                                                                    | 18 |

| FIG. 3.5: DEPLETION LAYER WIDTH AS A FUNCTION OF DOPING CONCENTRATION                                    | 19 |

| FIG. 3.6: SIMULATED BREAKDOWN VOLTAGE VS DOPING CONCENTRATION                                            | 19 |

| FIG. 3.7: Reverse characteristic                                                                         | 20 |

| FIG. 3.8: BREAKDOWN VOLTAGE AS A FUNCTION OF DOPING CONCENTRATION: NUMERICAL                             |    |

| SIMULATION VS ANALYTICAL CALCULATION                                                                     | 21 |

| FIG. 4.1: SCHEMATIC OF FIELD-PLATED DIODE                                                                | 23 |

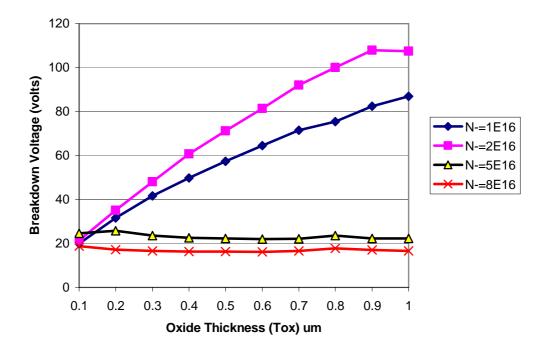

| FIG. 4.2: BREAKDOWN VOLTAGE VS OXIDE THICKNESS                                                           | 24 |

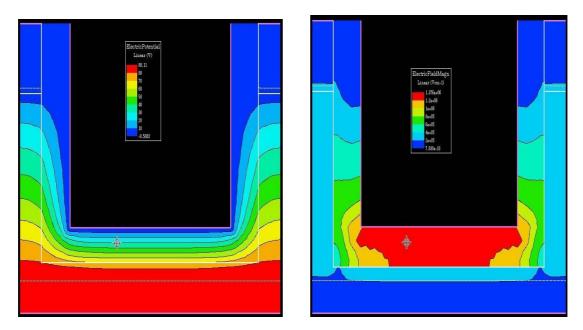

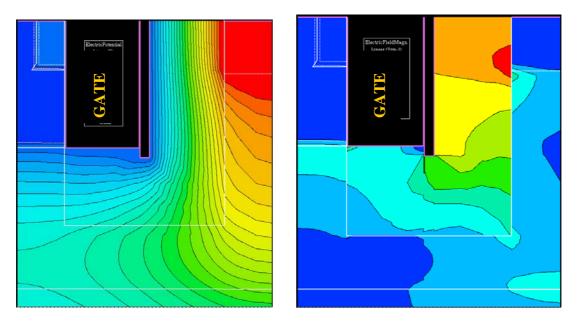

| FIG. 4.3: POTENTIAL DISTRIBUTION (LEFT) AND ELECTRICAL FIELD DISTRIBUTION (RIGHT) FOR .                  | AN |

| OPTIMAL DESIGN OF FIELD-PLATED DIODE; NDRIFT=2E16 CM <sup>-3</sup> , TOX=0.65 MICRONS                    | 25 |

| FIG. 4.4: POTENTIAL DISTRIBUTION (LEFT) AND ELECTRICAL FIELD DISTRIBUTION (RIGHT) FOR                    |    |

| NON-OPTIMAL DESIGN OF FIELD-PLATED DIODE; NDRIFT=5E16 CM-3, TOX=0.2 MICRONS                              | 25 |

| FIG. 4.5: BREAKDOWN VOLTAGE VS. DRIFT LENGTH                                                             | 26 |

| FIG. 4.6: COMPARISON GRAPH BETWEEN P-N JUNCTION AND FIELD-PLATED DIODE BREAKDOWN                         | [  |

| VOLTAGES FOR VARIOUS DOPING CONCENTRATIONS                                                               | 26 |

| FIG. 5.1: Hybrid diode schematic                                                                         |    |

| FIG. 5.2: BREAKDOWN VOLTAGE VS. OXIDE THICKNESS                                                          | 29 |

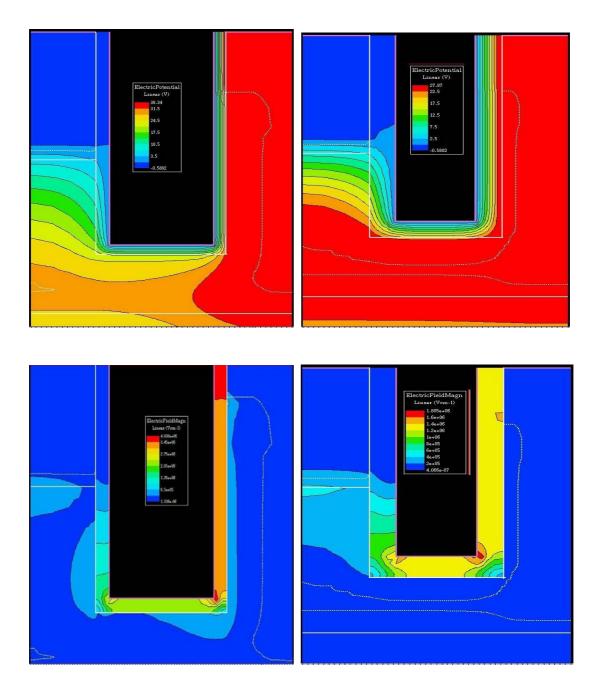

| FIG. 5.3: POTENTIAL (UPPER) AND ELECTRICAL FIELD (LOWER) DISTRIBUTION IN THE HYBRID                      |    |

| DIODE FOR NDRIFT=2E16CM <sup>-3</sup> AND DIFFERENT OXIDE THICKNESS: TOX=0.1MICRONS (LEF                 |    |

| AND 0.48 MICRONS (RIGHT)                                                                                 |    |

| FIG. 5.4: POTENTIAL (UPPER) AND ELECTRICAL (LOWER) DISTRIBUTION IN THE HYBRID DIODE F                    | OR |

| N drift =5E16 cm <sup><math>-3</math></sup> and different oxide thickness: Tox=0.1 microns (left) and 0. |    |

| MICRONS (RIGHT)                                                                                          |    |

| FIG. 5.5: BREAKDOWN VOLTAGE VS. OXIDE THICKNESS                                                          |    |

| FIG. 5.6: POTENTIAL AND ELECTRICAL FIELD DISTRIBUTIONS FOR 50V                                           |    |

| FIG. 5.7: BREAKDOWN VOLTAGE VS. OXIDE THICKNESS                                                          |    |

| FIG. 5.8: POTENTIAL AND ELECTRICAL FIELD DISTRIBUTIONS FOR 100V                                          |    |

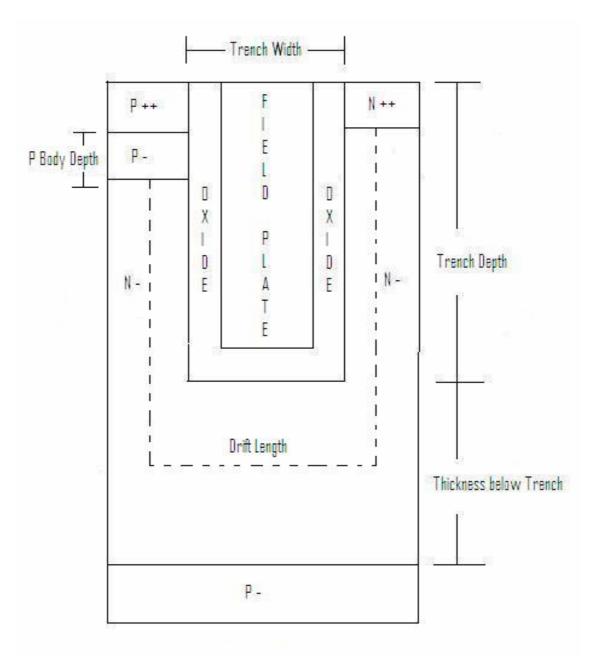

| FIG. 6.1: HYBRID NMOS TRANSISTOR SCHEMATIC                                                               |    |

| FIG. 6.2: BREAKDOWN VOLTAGE VS. DOPING CONCENTRATION                                                     |    |

| FIG. 6.3: BREAKDOWN VOLTAGE VS. OXIDE THICKNESS                                                          |    |

| FIG. 6.4: POTENTIAL AND ELECTRICAL FIELD DISTRIBUTIONS FOR OPTIMIZED 50V HYBRID NMC                      |    |

| TRANSISTOR                                                                                               |    |

| FIG. 6.5: ID-VG GRAPH FOR PWELL=6.7E17CM <sup>-3</sup> , VT=1V, 50V                                      |    |

| FIG. 6.6: BREAKDOWN VOLTAGE VS. DOPING CONCENTRATION                                                     |    |

| FIG. 6.7: BREAKDOWN VOLTAGE VS. OXIDE THICKNESS                                                          |    |

| FIG. 6.8: POTENTIAL AND ELECTRICAL FIELD DISTRIBUTIONS FOR OPTIMIZED 100V HYBRID NM                      |    |

| TRANSISTOR                                                                                               | 42 |

| FIG. 6.9: ID-VG GRAPH FOR PWELL=4.4E17 CM <sup>-3</sup> , VT=1V, 100V                                    |    |

| FIG. 6.10: COMPARISON OF $R_{ON, SP} - BV_{DS}$ trade-off for hybrid transistor and existing by          | CD |

| TECHNOLOGIES                                                                                             | 43 |

# LIST OF TABLES

| TABLE 3.1: P-N JUNCTION DIODE PARAMETERS                            | 18 |

|---------------------------------------------------------------------|----|

| TABLE 4.1: PARAMETERS USED FOR SIMULATION OF THE FIELD-PLATED DIODE | 23 |

| TABLE 5.1: HYBRID DIODE; SIMULATION PARAMETERS AND THEIR RANGE      | 27 |

| TABLE 5.2: OPTIMIZED HYBRID DIODE PARAMETERS (50V)                  | 32 |

| TABLE 5.3: OPTIMIZED HYBRID DIODE PARAMETERS (100V).                |    |

| TABLE 6.1: OPTIMAL PARAMETERS FOR 50V HYBRID NMOS TRANSISTOR        |    |

| TABLE 6.2: OPTIMAL PARAMETERS FOR 100V HYBRID NMOS TRANSISTOR       |    |

# **CHAPTER I INTRODUCTION**

#### **1.1 Overview of Power Devices**

The power devices play a vital role in current semiconductor technology. Many complex applications require power conversion (say DC-DC conversion). The need for long stand alone operating times and low power consumption when charging the battery, both require the use of efficient power converters. The application use of such high voltage devices can be generally divided into 2 categories; system-in-package (SiP) and system-on-chip (SoC). The SiP combines discrete high voltage components (produced by dedicated technology) with dedicated IC on separate printed boards. The high voltage discrete components are typically vertical devices produced by optimized technology often incompatible with IC processes (such as CMOS process). The SoC represents a solution, where the high voltage transistors are integrated in a silicon chip with the remaining IC components and produced in common IC manufacturing technology as a process option. The device concept under study described in this report targets the SoC solutions and therefore the SiP solutions and corresponding discrete HV device will not be considered.

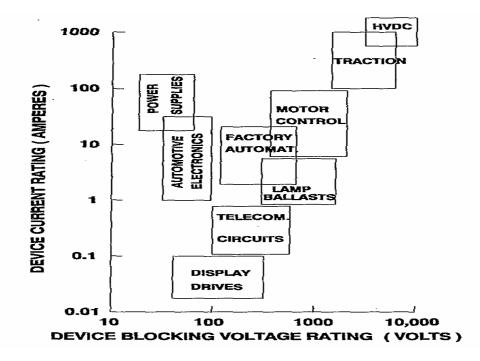

The integrated power devices have found various applications both in industrial and consumer equipments such as color television, mobile/static displays (cellular phones and portable music players), automotive electronics and telecommunication circuits (see Fig. 1.1). In these applications, the high-voltage transistors are typically used in the following circuits: DC-DC converters, display drivers or power management units. Most of these applications require blocking voltages in sub-200V regime and high current (<10 A) handling capability. The large current capability translates into a relatively large device size (i.e. long transistor width). As the cost per mm<sup>2</sup> of CMOS chip area ever increases, the low specific on-resistance (essentially determining the current handling capability per device area) is absolutely essential.

Fig. 1.1: Application of Power devices in relation to voltage and current ratings

# **1.2 Existing Solutions**

Different high voltage options embedded in various CMOS generations have been developed by several semiconductor companies. For example, ABCD (Advanced BiCmos Dmos) of Philips Semiconductors, BCD (BiCmos Dmos) of STMicroelectronics, LBC (Linear BiCmos) of Texas Instrument or SmartMOS offered by Freescale. In all these processes, the high voltage transistors are variants of lateral Double-diffused MOSFET (DMOS), also called extended-drain MOSFET. This type of transistor features a relatively lowly doped drift region separating the drain and gate in order to accommodate the high drain voltage. The gate channel and the drift region both expand in lateral direction (parallel to the silicon wafer surface). As a result the specific on-resistance is relatively large and strongly increases with the breakdown voltage.

To improve the trade-off between breakdown voltage and on-resistance, several Reduced Surface electrical Field (RESURF) methods are employed, e.g. junction RESURF or field plate based RESURF. These methods provides an enhanced depletion in the drift region, which in turn allows higher doping concentration there and thus lower on-resistance without breakdown voltage degradation.

# **1.3 Studied Device Concept**

In this work, a novel power MOSFET, Hybrid MOSFET, is studied. This structure features vertical drift region and vertical gate channel region, which allows maintaining the classical benefits of vertical devices. The breakdown voltage is enhanced by usage of field plate. However, all the device terminals (source, drain, gate and field plate) are located on top surface, which allows straightforward integration with IC processes.

This device construction is thoroughly analyzed with respect to different device parameters. Their influence on the potential distribution inside this novel device is evaluated and the corresponding breakdown voltage is determined. The structure is further optimized for relevant voltage range. These simulations were mainly realized on diodes. At the final stage, the results are verified also on transistors using the previously found optimal parameters. The performance analysis is completed by simulating also the on-state resistance. This allows to establish the breakdown voltage vs. specific on-resistance trade-off and to compare it to existing technologies.

# **1.5 Structure of the Report**

Chapter 1 outlines the background of this work and explains its scientific and industrial relevance.

Chapter 2 describes the simulation tools used in this project.

Chapter 3 discusses a normal 1-dimensional P-N junction diode and the simulated reverse characteristics.

Chapter 4 describes simulation results of field-plated diode and illustrates the influence of the field plate on breakdown voltage.

Chapter 5 introduces the hybrid diode structure. The influence of the different device parameters on its breakdown voltage is demonstrated. The optimization for 50 V and 100 V domains is discussed.

Chapter 6 evaluates the breakdown voltage and on-state characteristics of hybrid transistor (diode with added gate) and compares the achieved breakdown voltage vs. specific on-resistance with existing technologies.

Chapter 7 concludes the work and gives suggestions on the future work followed by abbreviations, symbols, references and appendix.

# **CHAPTER 2 SIMULATION TOOLS**

# **2.1 INTRODUCTION**

The commercially available simulation tools are either process or device simulators with an interface between them to allow device simulations with realistic process impact. These numerical simulators are mainly used for analytical and predictive purposes. They allow rather realistic insight into electronic device without a need to actually manufacture such device. Various physical parameters and phenomena can be analyzed at any location inside the device. This greatly reduces time and cost in semiconductor research and development, and enriches understanding of the device physics.

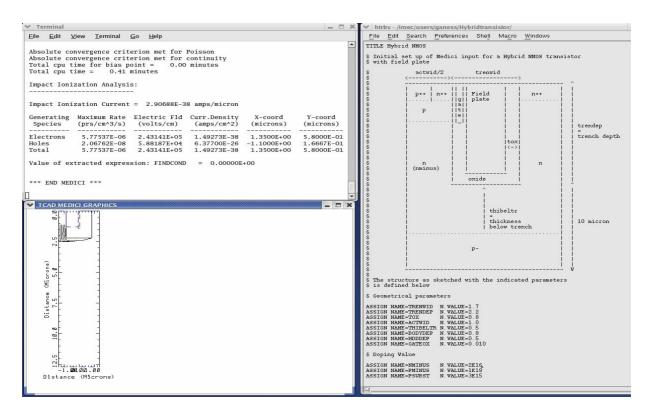

# 2.2 MEDICI 2D Device Simulation Program

The MEDICI software is a powerful device simulation program that is used to simulate many electronic devices, including diodes, MOSFETs, JFETs, bipolar transistors etc. This software allows 1-dimensional or 2-dimensional simulations. The simulated device is approximated with a mesh of discrete point emulating the device structure. The doping concentration, type of material and associated material and electrical constants are defined at each mesh points. During the structure definition, the electrodes (locations where voltage and current is applied and/or measured) are also defined. These can be realistic or completely arbitrary allowing a great flexibility in device analysis.

Once the structure definition is completed, an external potential can be applied and the program solves numerically Poisson equation and Continuity equation for electrons and holes. These equations can be solved separately or in combination. It is also possible to operate the device only with a single carrier, e.g. electrons. A number of physical models are incorporated for accurate description of physical phenomena, such as recombination, impact ionization, electrical field as a function of doping and surface scattering etc. Some details about the Medici tool related to our work are shown in the appendix section.

#### **2.3 Simulated Characteristics**

In the frame of this thesis report, four devices have been simulated. These are a simple 2D PN-junction (diode), field-plated diode, hybrid diode and hybrid transistor. The reverse characteristics are predominately simulated and breakdown voltage is established. The breakdown voltage is determined by evaluating impact ionization integral and the breakdown voltage is defined as a voltage where this integral reaches unity. These simulations are mainly based on solving Poisson equation only without considering carriers. This is in most cases sufficient and allows reducing substantially the computation time. In some particular structures, the electron and hole carriers are considered to ensure realistic results. This is indicated in the text, wherever appropriate. In case of the simple diode, the reverse current is also simulated, this

again requires carrier inclusion. This is purely to demonstrate the relevance of using the ionization integral for determining the breakdown voltage.

Finally, the hybrid transistor was simulated also in the on-state regime, where also the electron and hole carriers must have been taken into account to calculate the corresponding drain-source current.

.

# **CHAPTER 3** P-N Junction diode

### **3.1 Introduction**

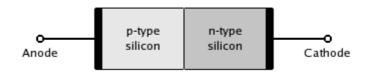

In order to establish the basic understanding of the breakdown voltage in semiconductor devices, a simple p-n junction will be studied initially. This study will be limited to reverse bias regime. A p-n junction diode is formed by combining N-type and P-type semiconductors, as illustrated in Fig. 3.1. The P-type and N-type regions are both homogeneously doped with step junction. The regions with the opposite sides of semiconductor join is usually called metallurgical junction.

Fig. 3.1: P-N Junction Diode.

In equilibrium state and no applied voltage (V=0V on anode and cathode), the majority carriers in both side of the junction diffuse to its opposite side to distribute uniformly throughout the entire material, i.e. holes from the p-side will diffuse into n-side and electrons from n-side to p-side. This diffusion process leads to charge imbalance (between fixed and mobile charges) on both sides of the junction. This charge imbalance produces an electrical field across the junction, which opposes the diffusion process so that the net flow of carriers is zero in thermal equilibrium. The space charge region, where the mobile carrier concentration is reduced below their thermal equilibrium value is called the depletion region.

The existence of the electrical field across the junction automatically implies existence of electrical potential across the depletion region, even though no external voltage was applied. This potential is called built-in potential and can be considered as similar to the contact potential between two metals.

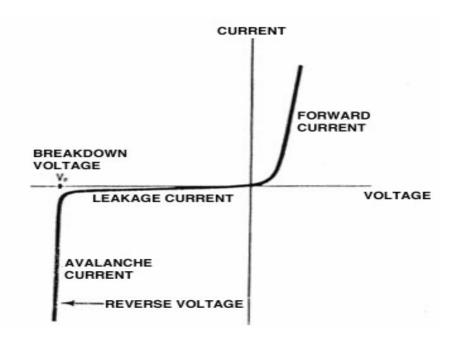

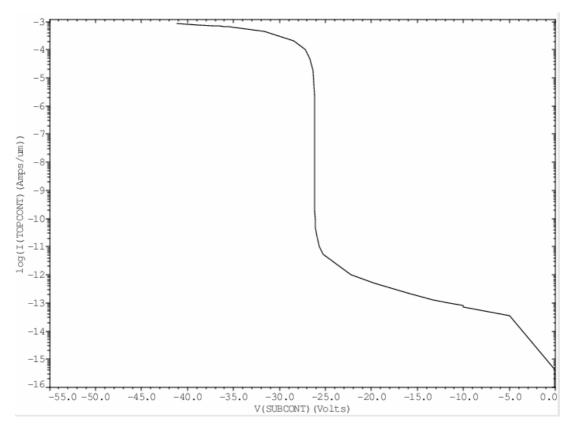

Under external bias, the potential barrier across the junction either reduces (forward bias regime) or increases (reverse bias regime) so that the current flow exponentially increases with applied voltage in the forward bias regime, while only minute current flows in the reverse bias regime. This small residual current (leakage current) is due to defects and other semiconductor imperfections. A typical I-V curve for a p-n junction is shown in Fig. 3.2.

Fig. 3.2: I-V Characteristics of a p-n junction diode.

#### 3.2 Breakdown Voltage

In order to analyze the device breakdown voltage it is necessary to analyze the breakdown characteristics of that device. The maximum reverse bias voltage that can be applied to a p-n diode is limited by breakdown. Breakdown is characterized by the rapid increase of the current under reverse bias. The corresponding applied voltage is referred to as the breakdown voltage showing that the device cannot withstand any further increase in voltage. The cause for breakdown in a device is due to the avalanche effect. The breakdown voltage occurring in a device is inversely proportional to the doping concentration (cm<sup>-3</sup>). Avalanche breakdown is caused by impact ionization of electron-hole pairs. When applying a high voltage the electric field increases, therefore the carriers gain kinetic energy and generate additional electron-hole pairs through impact ionization.

This process can be quantified through a parameter called the ionization integral. The ionization integral for a one dimensional p-n diode is given by:

$$I = \int_{0}^{W} \alpha(E) dx$$

Where x is the spatial coordinate, W the width of the depletion layer, E the electric field and  $\alpha$  the ionization coefficient.

Generally, avalanche breakdown occurs when the ionization integral reaches one i.e. unity. If the ionization integral is one then each electron generates another one and this leads to an avalanche breakdown. For this calculation it is enough if only the electric potential is considered and no need of electrons and holes. Therefore the carriers are set to 0 in our calculations.

$$1 - I = 0$$

or  $I = 1$

The above formula is for a one dimensional device structure. It shows that every ionization path is directed along a resultant electric field line and all paths yield the same ionization integral. If the electric field in the depletion region is two dimensional, not all ionization paths yield the same ionization integral and every possible path should be considered in calculating the breakdown voltage. The ionization integral first approaching unity determines the onset of breakdown voltage. The avalanche breakdown voltage of this one dimensional p-n junction diode is characterized by an effective ionization rate  $\alpha$ , defined as the average number of ionizing collisions encountered by a hole or electron per unit distance traveled in the field direction. The measurements of the ionization rates of electrons and holes in silicon p-n junction indicate that,

$$\alpha(E) = a. exp(-b/E)$$

(1)

where a=7.03E5 cm<sup>-1</sup> and b=1.468E6 Vcm<sup>-1</sup> for the electric field magnitude 1.75E5 <E<6.4E5 Vcm<sup>-1</sup> (ref: B.J. Baliga, Power Semiconductor Devices, pg. 67). The average number of ionizing collisions encountered by a single electron/hole crossing the depletion region is given by the ionization integral formula.

The avalanche breakdown voltage for a normal one dimensional p-n junction diode can be approximated using the following formula, (ref. B.J. Baliga, Power Semiconductor Devices, pg. 73)

$$Vbd = 5.34 \times 10^{13}$$

. (Na)<sup>-3/4</sup> (2)

where Vbd is the breakdown voltage and Na is the doping concentration.

This formula was derived under assumption of constant critical electrical field (independent of doping concentration) and depletion is assumed to propagate only in one side of the junction (e.g. N-type is lowly doped, while P-type is very heavily doped).

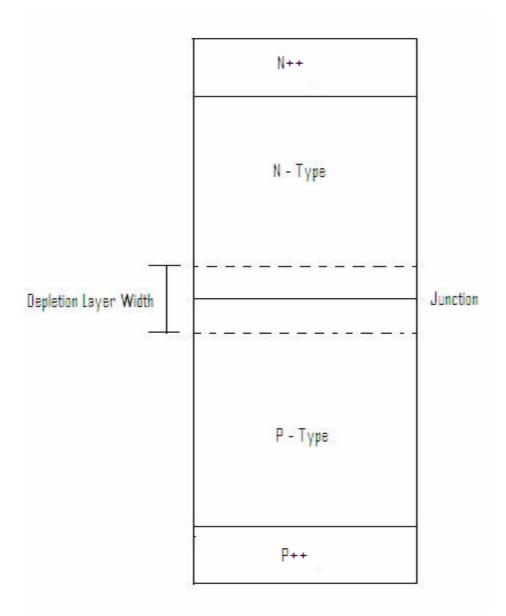

### 3.3 The Simulated Structure

Fig. 3.3: P-N junction diode schematic

The structure shown in Fig. 3.3 is a 2-dimensional P-N junction diode defined within the MEDICI simulation software. It consists of the N-type region (upper part) and P-type (lower part). Heavily doped N++ and P++ regions are established on the outsides of the diode for low ohmic connections. The exact diode parameters using the simulations are given in Table 3.1. The N-type is less doped as compared to P-type side and was designed longer to support the expansion of depletion layer and thus the high voltages. The anode and cathode electrodes are placed on the bottom and top of the device, respectively.

| Device Parameters       | Values                 |

|-------------------------|------------------------|

| Device width            | 2 µm                   |

| N-type depth            | 7.5 μm                 |

| N++ width               | 1.15 μm                |

| P-type width            | 5 μm                   |

| P++ width               | 1.15 μm                |

| N- region doping (N-)   | $1E17 \text{ cm}^{-3}$ |

| N++ region doping (N++) | $1E20 \text{ cm}^{-3}$ |

| P- region doping (P-)   | $2E17 \text{ cm}^{-3}$ |

| P++ region doping (P++) | $1E20 \text{ cm}^{-3}$ |

Table 3.1: P-N junction diode parameters

#### **3.4 Simulation and Analysis**

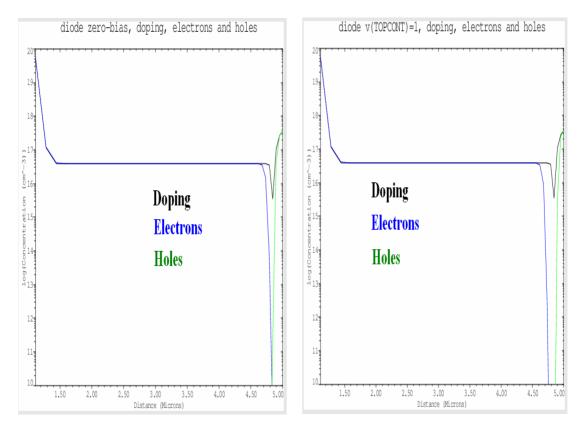

The 2-dimensional P-N junction diode was simulated with the above parameters and analyzed for different doping values. In this studied structure the doping concentration on one side of the junction is large when compared to the other side. For example the P region is doped more than the N- region. Therefore the depletion region extends primarily on the lightly doped side of the junction (N- region). This is illustrated in Fig. 3.4, where the carrier concentrations near the metallurgical junction are compared for zero volt bias and small reverse bias. As one can see, a larger portion of the N-type region is free of electrons.

Fig. 3.4: Doping, Electron and Hole concentration at zero bias (left) and reverse voltage of 1V (right).

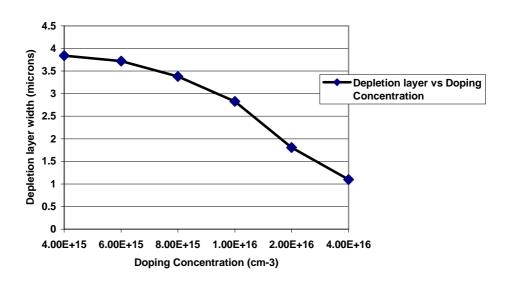

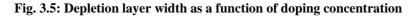

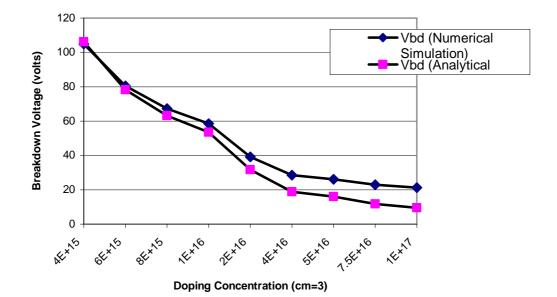

According to Eq.2, the breakdown voltage depends on the doping concentration in the less doped side of the junction. From the device simulation it is clear that the depletion region width is larger for junctions with lower doping concentration on the lightly doped side (see Fig. 3.5). The breakdown voltage was also determined for different doping concentrations as shown in Fig. 3.6. As an example, for a breakdown voltage of 80V, it is necessary to use a doping concentration for the lightly doped region of  $6E15 \text{ cm}^{-3}$ .

**Depletion layer Vs Doping Concentration**

Breakdown Voltage vs Doping Concentration (obtained)

Fig. 3.6: Simulated Breakdown voltage vs. Doping concentration

The previously discussed simulations were performed by solving only Poisson equation. In order to demonstrate the I-V characteristics in the reverse bias regime, further simulations were done assuming also electrons and holes. An example of such I-V characteristics is shown in Fig. 3.7.

The P++ region is connected to the negative terminal and the N++ type region to the positive terminal which therefore produces the reverse-bias effect. As the P-type region is now connected to the negative terminal of the power supply, the holes in the P-type region are pulled away from the junction, causing the width of the non conducting depletion zone to increase. Similarly, the N-type region is connected to the positive terminal; the electrons will also be pulled away from the junction. This effectively increases the potential barrier and greatly increases the resistance against the flow of charge carriers. Therefore there will be no current across the junction or crossing over the junction. At the middle of the junction of the p-n material, a depletion region is created to withstand the reverse voltage. But the width of this depletion region grows larger with increase in voltage. The electric field also increases as the reverse voltage increases. When the electric field increases beyond a critical level, the junction breaks down and current begins to flow due to avalanche breakdown. In this particular case, a breakdown voltage of approximately 25V is observed with a steep increase in current beyond this reverse voltage. Once a very large current is achieved, the current saturates again. This effect is associated with high-injection level and will not be discussed here.

Fig. 3.7: Reverse Characteristic

#### 3.5 Analytical vs Numerical results

In order to verify the simulated breakdown voltage values, we have compared them with values calculated using the analytical Eq.2. This comparison is shown in Fig. 3.8. The simulated data corresponds well with the analytical calculations. There is a small discrepancy at higher doping concentrations; here the simulated breakdown voltage is larger than the calculated values. This is due to the depletion layer in the P-side of the junction that is not taken into account in the analytical calculation, but it is present during simulation.

#### Vbd (Th, Obt) vs Doping Concentration

Fig. 3.8: Breakdown voltage as a function of doping concentration: numerical simulation vs. analytical calculation.

# CHAPTER 4 FIELD-PLATED DIODE

#### 4.1 Field Plate and Breakdown Voltage

In this chapter a concept of vertical diode with a field plate located in deep trench is described. The field plate is a conductive electrode placed in parallel with the drift region and insulated by a thick oxide layer from the drift region. The field plate is biased at zero voltage during the device operation. The grounded electrode is capacitively coupled to the drift region through the thick oxide. This results in depletion of the drift region near the interface with the oxide. This additional depletion layer joins with the depletion layer formed around the metallurgical junction of the diode. If the full length of the drift region is depleted (by the combined depletion layers), the total reverse voltage is distributed across the entire drift region length. This is typically much longer than the junction depletion width only. In a well designed device, a 20 V per micron of drift length can be supported. It is essential that the full depletion of the drift region must be achieved before the peak electrical field at the junction reaches the critical value.

The extra depletion layer due to the field plate action depends on several parameters; the drift region doping, the drift region width and the thick oxide layer thickness. The optimal doping concentration in the drift region can be calculated using the following equation,

$$N(x) = \frac{V}{W} \times \frac{\in o \in si}{qTs} \times \frac{1}{(Ts/2 + ((\in si/\in ox).Tox)))},$$

(3)

where V is the applied voltage, W the depletion layer width, Tox the oxide thickness and Ts the silicon width.

This chapter discusses numerical simulations performed with the field-plated diode varying the key parameters governing the breakdown voltage enhancement. As the hybrid diode/transistor employs the field plate, this provides basis for the hybrid device simulations.

#### 4.2 The simulated Structure

The field-plated diode structure shown in Fig. 4.1 is modeled with the device simulator MEDICI. This device has the basic structure of an ordinary P-N junction diode with highly doped P++ region on the top surface and moderately doped P-region with the lowly doped N-drift region below. The highly doped N++ region is at the bottom of the structure. The device differs from the previous by a field plate placed in a trench manner extending along the drift region and separated from it by a thick oxide (i.e. insulating layer). Since the lateral devices occupy more area, a vertical like structure is preferred. In order to obtain optimum field plate effect the device was simulated by altering the doping concentrations and oxide thickness and their breakdown voltage values were determined.

Fig. 4.1: Schematic of field-plated diode.

| Table 4.1: Parameters used for simulation | of the field-plated diode. |

|-------------------------------------------|----------------------------|

|-------------------------------------------|----------------------------|

| Device Parameters      | Values                                        |  |

|------------------------|-----------------------------------------------|--|

| Trench Depth           | 4 μm                                          |  |

| Drift Region length    | 3 µm                                          |  |

| Trench Width           | 5 µm                                          |  |

| Actual Width           | 1 μm                                          |  |

| Thickness below Trench | 0.25 μm                                       |  |

| N- drift region doping | 8E15, 1E16, 2E16, 5E16, 1E17 cm <sup>-3</sup> |  |

| P- body doping         | $1E18 \text{ cm}^{-3}$                        |  |

| Tox                    | $0.1-1.0~\mu m$                               |  |

#### 4.3 Simulation and Analysis

The key function of this RESURF technology is it enhances the depletion layer therefore obtaining a higher breakdown voltage. In order to optimize this RESURF effect the thickness of the oxide layer (Tox) and the drift region impurity concentration (Ndrift) are varied. The other important parameters are the drift region length and thickness below trench.

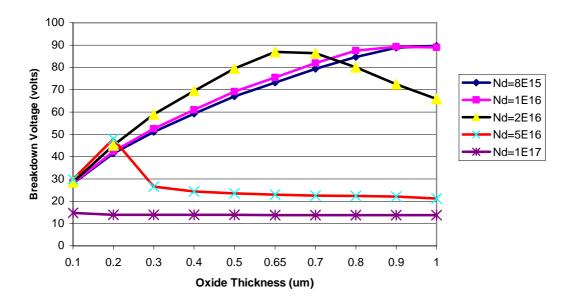

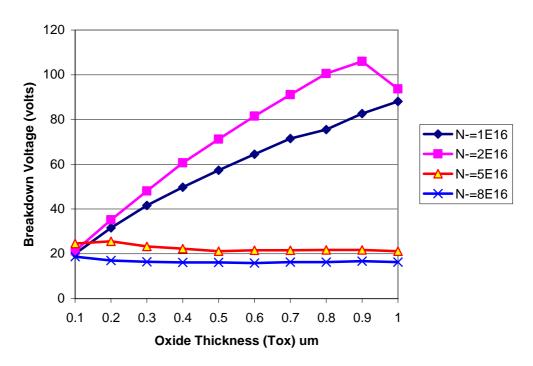

#### Breakdown Voltage vs Tox (for diff. dopings)

Fig. 4.2: Breakdown voltage vs. Oxide thickness.

Fig. 4.2 shows the simulated breakdown voltage as a function of oxide thickness for different values of drift region doping. It clearly illustrates an optimum in oxide thickness to reach maximal breakdown voltage. For Tox smaller than optimum, the breakdown voltage is limited by the potential sustainable across this oxide layer. For Tox larger than optimum, the capacitive coupling is too weak to deplete the full drift region. There is also an optimal doping concentration of the drift region. Ndrift larger than optimal prohibit full depletion of the drift region before critical electrical field is reached.

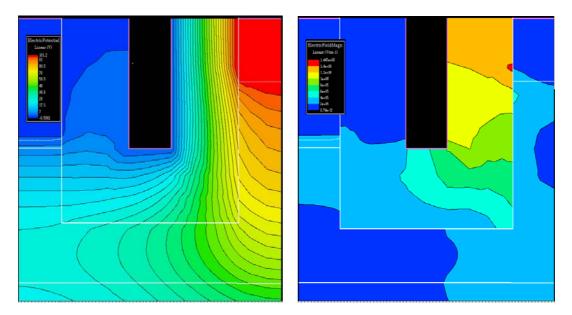

This is further illustrated by plotting the potential and electrical field map inside the device. In case of an optimal field-plated device (see Fig. 4.3), the complete drift region is depleted (the depletion is seen by the dotted line), the equipotential lines are uniformly distributed and a constant electrical field is obtained along the drift region. In case of non-optimal field-plate device (too large doping, see Fig. 4.4), the drift region is not completely depleted before critical electrical field is reached and an early breakdown voltage is observed.

Fig. 4.3: Potential distribution (left) and electrical field distribution (right) for an optimal design of field-plated diode; Ndrift=2E16 cm<sup>-3</sup>, Tox=0.65 microns.

Fig. 4.4: Potential distribution (left) and electrical field distribution (right) for non-optimal design of field-plated diode; Ndrift=5E16 cm<sup>-3</sup>, Tox=0.2 microns.

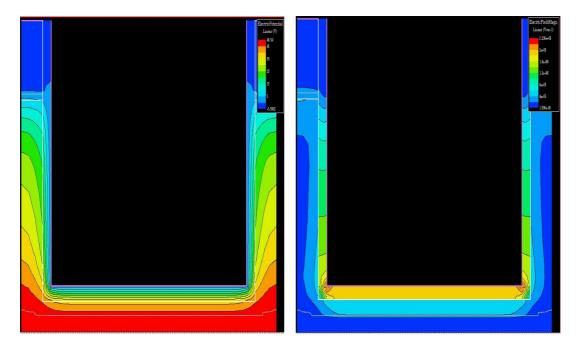

As discussed earlier, the drift length also has an impact in the breakdown voltage. The device was simulated by altering the drift length and keeping all other parameters constant. The simulation results show that by increasing the drift length the breakdown voltage also is increased (see Fig. 4.5).

Breakdown Voltage vs Length (for opt. Tox=0.65um & diff. Nd doping)

Fig. 4.5: Breakdown voltage vs. drift length.

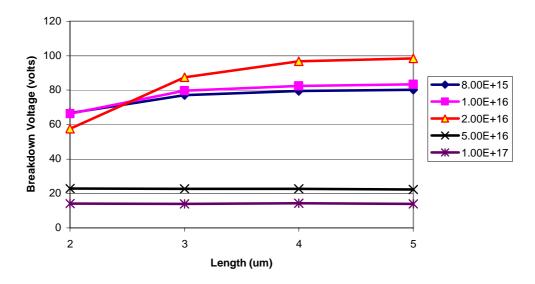

#### 4.4 Normal diode vs. Field-Plated diode

Fig. 4.6: Comparison graph between P-N junction and field-plated diode breakdown voltages for various doping concentrations.

From the above figure it is clear that we have obtained a higher breakdown voltage in the field-plated diode using RESURF concept than the normal diode.

It has been shown that device with optimal parameters can withstand a maximum voltage of 87 V for a doping concentration of 2E16 and 0.65  $\mu$ m oxide thickness.

# CHAPTER 5 HYBRID DIODE

# 5.1 Hybrid high voltage device: Introduction

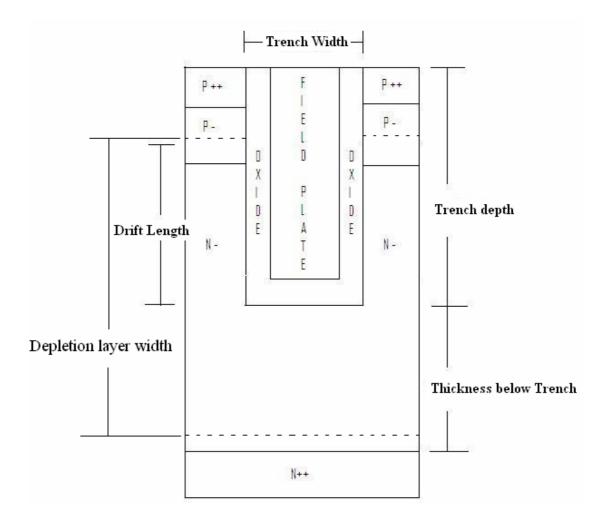

In this chapter a hybrid diode vertical in structure with the field plate effect is discussed. The hybrid device feature again a field plate located in deep trench and insulated from the drift region by a thick oxide layer. Differently from the classical vertical field-plated device (see Chapter 4), the drain is located on top surface and the drift region stretches along the trench. So that the current flows downwards, under the trench and upwards again along the trench sidewalls, where it enters the vertical gate channel. This full vertical current flow is expected to yield a transistor with high voltage capability and very compact size.

In order to study the blocking voltage capability of the hybrid device, it is sufficient to investigate a hybrid diode, which is essentially identical to hybrid transistor, but does not include gate. The device was simulated for various parametric values. It was finally optimized to obtain breakdown voltages up to 50V and 100V.

# **5.2 The Simulated Structure**

The hybrid diode has a similar structure like the previous vertical diode with field plate placed in a trench manner. Here the  $N_{++}$  region is at the top (right) with N- drift region stretching along the field plate. The  $P_{++}$  region and medium doped P body region are located at the top (left) remains the same as in the classical field-plated diode. The lowly doped P- substrate is at the bottom of the device structure and is connected to ground via a bottom electrode. Table 5.1 lists the parameters that were varied in the simulations. It also gives their range used to optimize the voltage blocking capability.

| Hybrid diode parameters | Range of values               |

|-------------------------|-------------------------------|

| Trench width            | 0.8 - 5 μm                    |

| Trench depth            | 0.95 - 5 μm                   |

| Actual width            | 1 μm                          |

| Thickness below trench  | 0.1- 0.9 μm                   |

| N- drift region doping  | $1E14 - 1E17 \text{ cm}^{-3}$ |

| P- (body depth) doping  | $1E18 \text{ cm}^{-3}$        |

| P substrate doping      | $3E15 \text{ cm}^{-3}$        |

| Тох                     | $0.05 - 0.48 \ \mu m$         |

| Drift length            | 3-14 μm                       |

| Table 5.1: Hybrid | diode; simulation | parameters and | their range. |

|-------------------|-------------------|----------------|--------------|

|-------------------|-------------------|----------------|--------------|

Fig. 5.1: Hybrid diode schematic.

#### 5.3 Simulation and Analysis:

In this section the hybrid diode device simulated by altering the device parameters for different doping concentrations, oxide thicknesses, trench width and trench depth will be discussed in detail. The device was simulated varying oxide thickness (Tox) and drift region doping concentration (N drift). Other parameters were kept constant. In most cases, it was sufficient to solve only Poisson equation without using carriers. For high doping concentration of the drift region (N drift >= 5e16 cm<sup>-3</sup>), the particular structure construction leads to floating islands surrounded by fully depleted regions. In such case, the simulation included also continuity equations for electrons and holes to guarantee correct results.

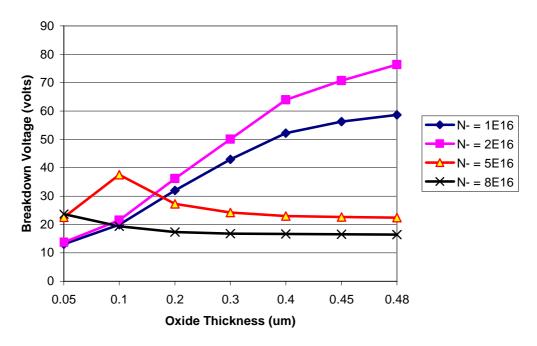

# Vbd vs Tox ( for diff. N- doping)

Fig. 5.2: Breakdown voltage vs. Oxide thickness.

The breakdown voltage as a function of Tox and Ndrift is shown in Fig. 5.2. As one can see, the Ndrift =  $2e16 \text{ cm}^{-3}$  is an optimal value for the drift region doping and there is an optimal oxide thickness leading to the highest breakdown voltage. For better understanding of mechanisms responsible for the breakdown voltage at different design parameters, we have studied the potential and electrical field distribution inside the hybrid diode.

For Ndrift =  $2e16 \text{ cm}^{-3}$  (see Fig. 5.3), one can see that the full drift region is depleted for Tox = 0.1 microns as well as for Tox = 0.48 microns. The potential is distributed almost linearly on both sides of the trench as well as underneath the trench, which is very good. The electrical field distribution indicates that the critical electrical field is reached under the drain (top right corner of the device) near the interface with the thick oxide. This is because the thick oxide has to withstand the full voltage between drain (on high voltage) and field plate (zero voltage). The oxide itself is sufficiently thick to withstand such voltage difference, but due to the permittivity difference between oxide and silicon, the electrical field in silicon at the interface exceeds the critical value. Clearly, further increase in oxide thickness will reduce this bottleneck and even higher breakdown voltage will be achieved. However, the field plate effect reduces with a thicker oxide. Once the oxide thickness exceeds optimal value, the breakdown voltage will decrease again due to loss of the field plate coupling.

Fig. 5.3: Potential (upper) and electrical field (lower) distribution in the hybrid diode for Ndrift=2E16 cm<sup>-3</sup> and different oxide thickness: Tox=0.1microns (left) and 0.48 microns (right).

For N drift =  $5e16 \text{ cm}^{-3}$  (see Fig. 5.4), one can see that the drift region is only partially depleted and the field plate action is insufficient. The potential is distributed only under the P-body/N-drift junction on the left handside of the trench and the critical electrical field is reached at this junction, which causes the breakdown.

Fig. 5.4: Potential (upper) and electrical (lower) distribution in the hybrid diode for N drift =5E16 cm<sup>-3</sup> and different oxide thickness: Tox=0.1 microns (left) and 0.2 microns (right)

## 5.4 Hybrid Diode for 50 V domain

In this section the hybrid diode device optimized for 50V will be discussed. The optimal values leading to the most compact 50 V hybrid diode are listed in Table 5.2. Providing the optimal oxide thickness of 0.3  $\mu$ m, the trench width can actually be further reduced.

| Optimized diode parameters | Values                 |

|----------------------------|------------------------|

| Trench width               | 0.8 μm                 |

| Trench depth               | 1.0 μm                 |

| Oxide thickness            | 0.3 μm                 |

| Actual width               | 1.0 μm                 |

| Thickness below Trench     | 0.5 μm                 |

| Body depth                 | 0.3 μm                 |

| N- (drift region) doping   | $2E16 \text{ cm}^{-3}$ |

| P- (body) doping           | $1E18 \text{ cm}^{-3}$ |

| P substrate doping         | $3E15 \text{ cm}^{-3}$ |

| Drift length               | 2.02 μm                |

Table 5.2: Optimized hybrid diode parameters (50V)

Fig. 5.5: Breakdown voltage vs. Oxide thickness.

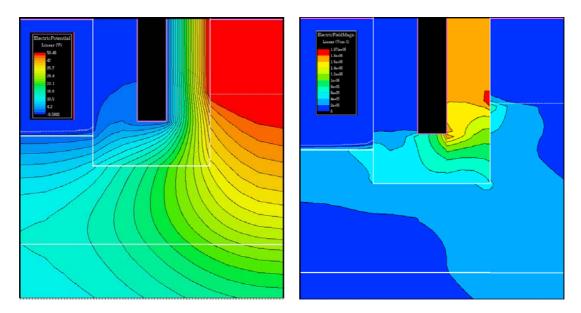

An example of the optimization process is shown in Fig. 5.5, where breakdown voltage is plotted as a function of oxide thickness. The optimal oxide thickness of 0.3  $\mu$ m is clearly observed. Finally, Fig. 5.6 shows potential and electrical field distribution in the optimized 50 V hybrid diode. The potential is almost linearly distributed along all three sides of the trench and the highest electrical fields are observed at the P-body/N-drift junction and under the drain.

Fig. 5.6: Potential and Electrical field distribution for 50V.

# 5.5 Hybrid Diode for 100 V domain

In this section the hybrid diode device optimized for 100V is discussed. The optimized values of design parameters for 100 V operations are listed in Table 5.3. Providing the optimal oxide thickness of 0.8  $\mu$ m, the trench width can actually be further reduced.

| Optimized diode parameters | Values                 |

|----------------------------|------------------------|

| Trench width               | 2.1 μm                 |

| Trench depth               | 2.1 μm                 |

| Oxide thickness            | 0.8 μm                 |

| Actual width               | 1.0 μm                 |

| Thickness below trench     | 0.5 μm                 |

| Body depth                 | 0.8 μm                 |

| N- (drift region) doping   | $2E16 \text{ cm}^{-3}$ |

| P- (body) doping           | $1E18 \text{ cm}^{-3}$ |

| P substrate doping         | $3E15 \text{ cm}^{-3}$ |

| Drift length               | 4.94 μm                |

Vbd vs Tox (for diff. N- doping)

Fig. 5.7: Breakdown voltage vs. Oxide thickness.

An example of the optimization process is shown in Fig. 5.7, where breakdown voltage is plotted as a function of oxide thickness. The optimal oxide thickness of 0.8-0.9  $\mu$ m is clearly observed. Finally, Fig. 5.8 shows potential and electrical field distribution in the optimized 100 V hybrid diode. The potential is almost uniformly distributed along all three sides of the trench and the highest electrical fields are under the drain.

Fig. 5.8: Potential and Electrical field distributions for 100V.

## **5.6 Conclusion**

A simple hybrid diode was simulated and the influence of different parameters on the breakdown voltage was studied. The studied parameters were trench width, trench depth, oxide thickness, drift length and doping concentration. The device was optimized for 50V and 100V operations. Here the optimal doping concentration value was found to be 2E16 cm<sup>-3</sup> and optimal oxide thickness of 0.3  $\mu$ m (50V) and 0.8 $\mu$ m (100V) was found.

### **CHAPTER 6 HYBRID TRANSISTOR**

#### **6.1 Introduction**

As the future power integrated circuits for power management and automotive electronics requires integration of power electronic components into advanced CMOS technology processes, a novel hybrid transistor is analyzed in this chapter. The hybrid transistor is based on the hybrid diode discussed in the previous chapter. It further includes gate and source region. The design parameters optimized for the hybrid diode for 50 V and 100 V operations were used for the simulations of the hybrid N-channel transistor. It was verified that the hybrid transistor and hybrid diode exhibit essentially identical breakdown voltages for identical design parameters. Furthermore, the hybrid transistor was optimized for a threshold voltage of 1 V and a specific onresistance was determined. The best values of  $BV_{DS} - R_{on,sp}$  for hybrid transistor were benchmarked against the state-of-the-art lateral integrated transistors.

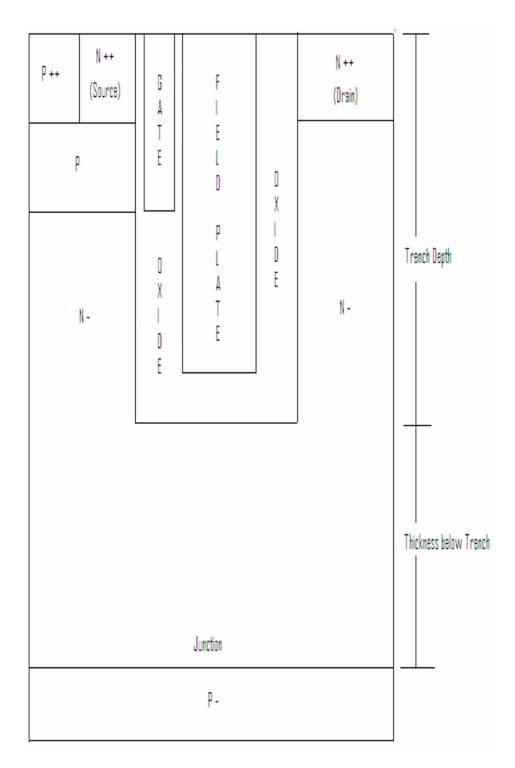

#### 6.2 The simulated Structure

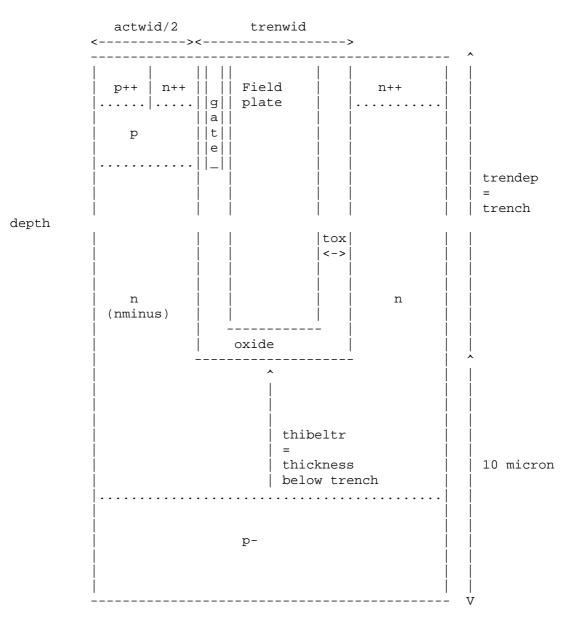

Fig. 6.1 shows the two dimensional view of the hybrid transistor simulated using the MEDICI simulator. The source, drain, gate, field plate and body contacts are on the top surface of the device. This device consists of a vertical trench with a field plate insulated from the drift region by a thick oxide (Tox). In the subtrench on the left handside of the original trench is located gate, which is separated from the transistor channel and from the field plate by a thin gate oxide (Tgox). The drain (N++) is located on the right-hand side, while source (N++) and body contact (P++) are located on the left-hand side. The source and body are sharing a common electrode. The N-drift region stretches along the trench sidewalls and the P body region is located in the upper left handside and aligned in depth with the gate. The breakdown voltage was simulated for different values of trench width, trench depth, drift length, oxide thickness, thickness below trench and doping concentration.

Fig. 6.1: Hybrid NMOS Transistor schematic.

### 6.3 Simulation Results and Analysis

#### 6.3.1 50V Hybrid transistor: off-state characteristics

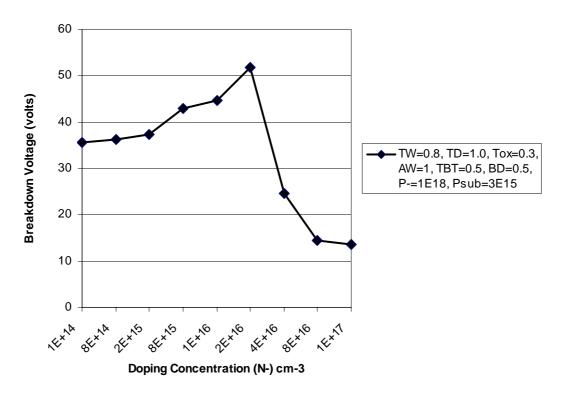

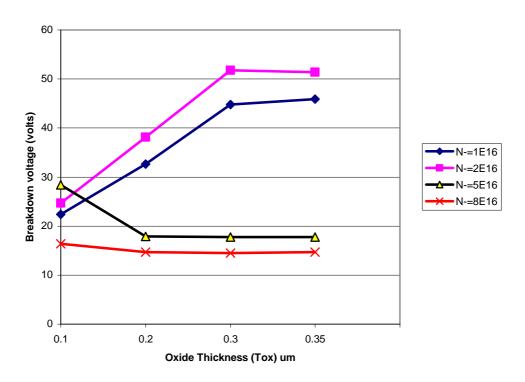

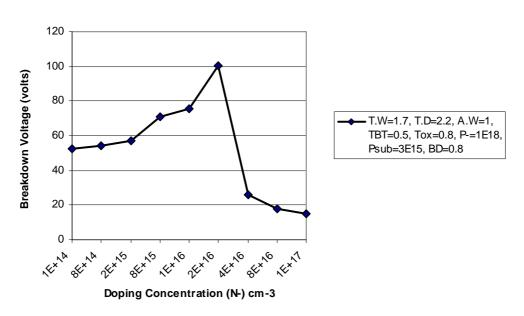

The trends in breakdown voltage dependence on the device parameters simulated for hybrid diode for 50 V domain were verified also for the hybrid NMOS transistor. Fig. 6.2 shows the breakdown voltage as a function of doping concentration. One can see a clear optimum for a Ndrift =  $2e_{16}$  cm<sup>-3</sup>. Providing the drift region width of 1 micron, the optimal doping dose of the drift region is  $2e_{12}$  cm<sup>-2</sup>. This corresponds very well with the ideal double-sided RESURF dose (mirrored stripe configuration).

Doping Concentration (N-) vs Breakdown Voltage

Fig. 6.2: Breakdown voltage vs. Doping concentration.

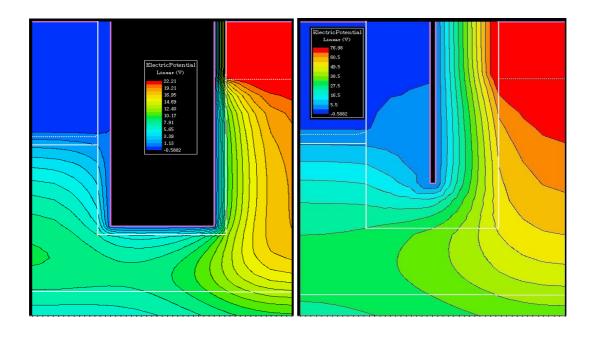

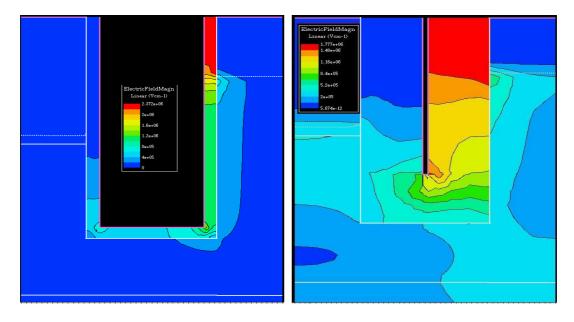

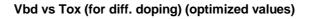

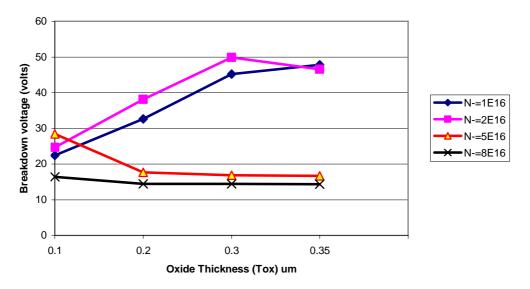

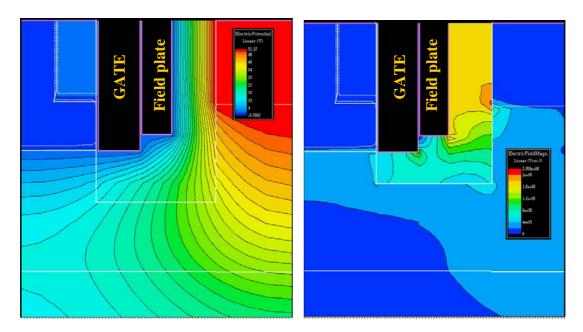

Fig. 6.3 shows breakdown voltage as a function of oxide thickness Tox. For an optimal drift region doping concentration, the highest breakdown voltage is achieved for Tox=0.3  $\mu$ m. For Tox larger than 0.3 $\mu$ m, the field plate influence reduces due to weaker capacitive coupling. The optimal design parameters for hybrid NMOS transistor for 50 V domain are summarized in Table 6.1. The simulated potential and electrical field distributions of the optimal 50 V hybrid NMOS transistor are shown in Fig. 6.4.

Vbd vs Tox (for diff. doping)

Fig. 6.3: Breakdown voltage vs. Oxide thickness.

| Transistor Parameters (50V) | Values                 |

|-----------------------------|------------------------|

| Trench width                | 0.8 μm                 |

| Trench depth                | 1.0 μm                 |

| Oxide thickness             | 0.3 μm                 |

| Actual width                | 1.0 μm                 |

| Thickness below Trench      | 0.5 μm                 |

| Body depth                  | 0.3 μm                 |

| N++/P++                     | 0.5 μm                 |

| Gate oxide                  | 0.010 μm               |

| N- (drift) doping           | $2E16 \text{ cm}^{-3}$ |

| P- doping                   | $1E18 \text{ cm}^{-3}$ |

| P substrate doping          | $3E15 \text{ cm}^{-3}$ |

Table 6.1: Optimal parameters for 50V hybrid NMOS transistor

Fig. 6.4: Potential and Electrical field distributions for optimized 50V hybrid NMOS transistor.

#### 6.3.2 50 V Hybrid transistor: on-state characteristics

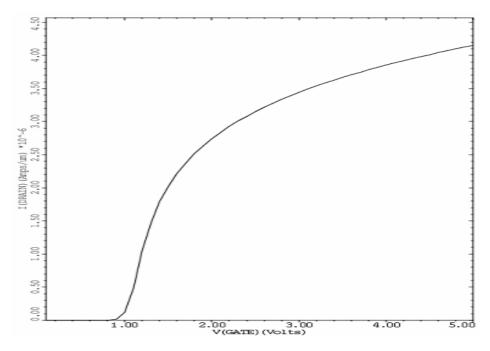

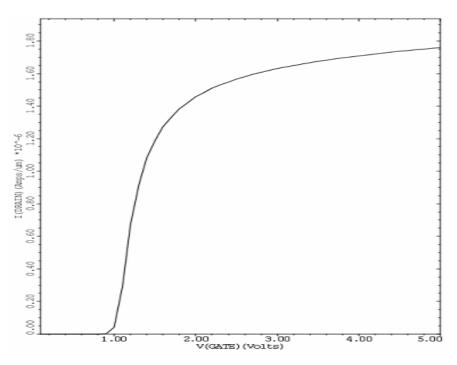

As a basic on-state characteristic, a drain current as a function of gate voltage was simulated. Fig. 6.5 shows the Id -Vg curve for a drain voltage of 0.05 V. The body doping was 6.7E17 cm<sup>-3</sup> and it was chosen to achieve a threshold voltage of 1 V. The simulated current allows us to determine the specific on-resistance. We found a specific on-resistance of Ron,sp =  $21.7 \text{ m}\Omega$ .mm<sup>2</sup> for Vg=5V.

Fig. 6.5: Id-Vg graph for Pwell=6.7E17 cm<sup>-3</sup>, Vt=1V, 50V.

#### 6.3.3 100V Hybrid transistor: off-state characteristics

The breakdown voltage as a function of drift region doping concentration and oxide thickness doping are shown in Fig. 6.6 and 6.7, respectively. The optimal doping concentration is again  $2e_{16}$  cm<sup>-3</sup> and an optimal oxide thickness is 0.8 microns. The optimal parameters for 100 V NMOS device are summarized in Table 6.2.

Doping Concentration (N-) vs Breakdown Voltage

Fig. 6.6: Breakdown voltage vs. Doping concentration.

Vbd vs Tox (for diff. N- doping)

Fig. 6.7: Breakdown voltage vs. Oxide thickness.

| Transistor Parameters (100V) | Values                 |

|------------------------------|------------------------|

| Trench width                 | 1.7 μm                 |

| Trench depth                 | 2.2 μm                 |

| Oxide thickness              | 0.8 µm                 |

| Actual width                 | 1.0 μm                 |

| Thickness below Trench       | 0.5 μm                 |

| Body Depth                   | 0.8 µm                 |

| N++/P++                      | 0.5 μm                 |

| Gate oxide                   | 0.010 µm               |

| N- (drift) doping            | $2E16 \text{ cm}^{-3}$ |

| P- doping                    | $1E18 \text{ cm}^{-3}$ |

| P substrate doping           | $3E15 \text{ cm}^{-3}$ |

Table 6.2: Optimal parameters for 100V hybrid NMOS transistor

The potential and electric field distribution for the optimized 100 V hybrid NMOS transistor are shown in Fig. 6.8. The potential distribution is nearly ideal linear in the drift region around the whole trench. The voltage handling capability is limited by the high electrical field under the drain.

Fig. 6.8: Potential and Electrical field distribution for optimized 100V hybrid NMOS Transistor.

## 6.3.4 100 V Hybrid transistor: on-state Characteristics

The drain current versus gate voltage was simulated for the optimized 100 V hybrid NMOS transistor and Id-Vg curve for Vd = 0.05 V is shown in Fig. 6.9. The threshold voltage is approximately 1 V. We have determined a specific on-resistance of 76.7 m $\Omega$ mm<sup>2</sup>.

Fig. 6.9: Id-Vg graph for Pwell=4.4E17 cm<sup>-3</sup>, Vt=1V, 100V.

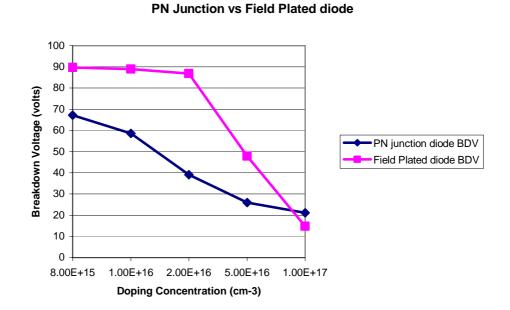

### 6.4 Benchmarking

The studied hybrid NMOS transistor optimized for 50V and 100V was compared with current best-in-class lateral BCD technologies in Fig. 6.10. The simulated hybrid NMOS features Ron,sp = 21.7 m $\Omega$ mm<sup>2</sup> for 50V and Ron,sp=76.7 m $\Omega$ mm<sup>2</sup> for a 100V domain, respectively. The hybrid transistor outperforms significantly all existing solutions.

Fig. 6.10: Comparison of Ron, sp - BVds trade-off for hybrid transistor and existing BCD technologies

## CHAPTER 7 CONCLUSION

## 7.1 PRESENT WORK

In this work, a novel hybrid transistor for future power integrated circuits was proposed. This concept aims to enhance scaling of power transistors. The device was optimized for two different breakdown voltages (50V, 100V) and very good results were obtained from the simulation.

A specific on-resistance of 21.7 m $\Omega$ mm<sup>2</sup> and 76.7 m $\Omega$ mm<sup>2</sup> is obtained for 50 V and 100 V domain, respectively. This is significantly better than all existing BCD technologies.

## 7.2 FUTURE WORK

The possible work which can be carried out on this project in the future is by further optimizing the device for 25V, 75V, 125V and 150V respectively by altering the parameters discussed in this work. Therefore this device can be used for all sort of low voltage applications. It can also become the key component in all power integrated circuits.

## **LIST OF ABBREVIATIONS**

| ABCD –   | Advanced BiCMOS DMOS                              |

|----------|---------------------------------------------------|

| BCD –    | BiCMOS DMOS                                       |

| CMOS –   | Complementary Metal Oxide Semiconductor           |

| DMOS –   | Double Diffused MOS                               |

| IC –     | Integrated Circuit                                |

| JFET –   | Junction Field Effect Transistor                  |

| LDMOS –  | Lateral Double diffused MOS                       |

| MOSFET – | Metal Oxide Semiconductor Field Effect Transistor |

| NMOS -   | N-type MOS                                        |

| PIC –    | Power Integrated Circuits                         |

| PMOS -   | P-type MOS                                        |

| PN –     | P-type and N-type junction                        |

| RESURF – | Reduced Surface Field                             |

| SOI –    | Silicon on Insulator                              |

|          |                                                   |

2D – Two Dimensional

## LIST OF SYMBOLS

| K -         | Boltzmann's constant (1.38 x 10 <sup>-23</sup> Joule/Kelvin)   |

|-------------|----------------------------------------------------------------|

| L -         | Length (m)                                                     |

| N++ -       | Highly doped N region (cm <sup>-3</sup> )                      |

| N           | Lightly doped N region (cm <sup>-3</sup> )                     |

| Nd –        | <b>Doping Concentration</b> ( <i>cm</i> <sup>-3</sup> )        |

| P++ -       | Highly doped P region (cm <sup>-3</sup> )                      |

| P           | Lightly doped P region (cm <sup>-3</sup> )                     |

| q-          | Electronic charge (1.602 x 10 <sup>-19</sup> Coulomb)          |

| <b>R</b> –  | Resistance (ohm)                                               |

| Rds, on –   | on state drain source resistance $(m \Omega.mm^2)$             |

| Rsp –       | Specific on-resistance $(m \Omega.mm^2)$                       |

| Tox –       | Oxide Thickness (m)                                            |

| Ts –        | Silicon thickness (m)                                          |

| <b>V</b> -  | Applied voltage (volt)                                         |

| Vbd -       | Breakdown Voltage (volt)                                       |

| Vd -        | Drain Voltage (volt)                                           |

| Vg –        | Gate Voltage (volt)                                            |

| Vt –        | Threshold Voltage (volt)                                       |

| <b>W</b> -  | Width of the depletion layer (m)                               |

| Х -         | Spatial co-ordinate                                            |

| α-          | Ionization coefficient                                         |

| <i>∈0</i> - | Permittivity of vacuum (8.854 x 10 <sup>-12</sup> Farad/meter) |

| $\in si$ -  | Dielectric constant of silicon (11.7) (F/m)                    |

| $\in ox$ -  | Dielectric constant of oxide (3.8) (F/m)                       |

#### **REFERENCES**

- Bimal K. Bose, "Evaluation of Modern Power Semiconductor devices and future trend of Converters", IEEE Transactions on Industrial Applications, Vol. 28, No. 2, March/April 1992.

- 2) **B.J. Baliga,** "*Power Semiconductor Devices*", pg. 67 and 73.

- 3) Claudio Contiero, Antonio Andreini, Paolo Galbiati, "Roadmap Differentiation and Emerging Trends in BCD Technology, ESSDERC 2002.

- 4) **Peter van DerVoorn, Dong Gan**, and **J. Peter Krusius**, "*CMOS Shallow Trench Isolation to 50 nm channel widths*", IEEE Transactions on Electron Devices, VOL 47, No.6, June 2000.

- M. Badila, Gh. Brezeneanu, "Field Plate Termination for Schottky Structure", Proc. 20<sup>th</sup> International Conference on Microelectronics (MIE695), Vol. 1, Serbia, 12-14 September, 1995.

- 6) **D. Jaume, G. Gharitat, J.M. Reynes and P. Rossel,** *"High Voltage Planar Devices using Field Plate and Semi-Resistive Layers"*, IEEE Transactions on Electron Devices, Vol. 38, No. 7, July 1991 pg. 1681-1684.

- Steve Merchant, "Analytical Model for the Electric Field Distribution in SOI RESURF and TMBS Structures", IEEE Transactions on Electron Devices, Vol. 46, No. 6, June 1999, pg. 1264-1267.

- 8) Sang-Koo Chung and Seung-Youp Han, "Analytical Model for the Surface Field Distribution of SOI RESURF Devices", IEEE Transactions on Electron Devices, Vol. 45, No. 6, June 1998, pg. 1374-1376.

- 9) **David J. Walkey**, MOSFET Operation (21), "*Physical Electronics*", 97.398\*, Lecture 21.

- 10) D.R. Disney, A.K. Paul, M. Darwish, R. Basecki, V. Rumennik, "A new 800V lateral MOSFET with dual conduction paths", Proceedings of 2001 International Symposium on Power Semiconductor Devices and IC's, Osaka, 10.3, pg. 399-402.

- Mohamed N. Danvish and M. Ayman Shibib, "Lateral MOS Gated Power Devices – A Unified View", IEEE Transactions on Electron Devices, Vol. 38, No. 7, July 1991, pg. 1600-1604.

- 12) Jess Brown, Guy Moxey, "Power MOSFET Basics: Understanding MOSFET Characteristics Associated with the Figure of Merit (FOM), Vishay Siliconix, AN 605, Doc. No. 71933.

- 13) **Vrej Barkhordarian**, "*Power MOSFET Basics*", International Rectifier, El Segundo, CA.

- 14) Amit Paul and Donald Ray Disney, "High Voltage Lateral transistor with a multi-layered extended drain Structure", United States Patent, 868984, June 16, 2004, Power Integrations, Inc.

- 15) Apples and Vaes, "High Voltage Thin Layer Devices (RESURF Devices)", IEDM Tech Digest, Dec. 3-4-5, 1979, pp 238-241.

- 16) **S. Merchant et al.**, "*Realization of High Breakdown Voltage* (>700V) *in Thin SOI Devices*", 1991 IEEE, pp 31-35.

- 17) Anaman, et al., "Comparison of High-Voltage Devices for Power Integrated Circuits", IEDM 84, pp 258-261.

- 18) **Sze, et al.,** *"Modern Semiconductor Device Physics,"* John Wiley & Sons, Chapter 4 ("Power Devices"), 1998, pp 203-206.

- 19) Hamza Yilmaz, "Modeling and Optimization of Lateral High Voltage IC Devices to Minimize 3-D Effects", United States Patent 6768172, R&D Engineering, General Electric Co., NC, pp 290-294.

- 20) **Chen et al.**, "*Optimization of the Specific On-Resistance of the COOLMOS*, IEEE Transactions on Electron Devices, vol. 48, No. 2, Feb. 1, pp 344-348.

- 21) Masakazu Kanechika, Masahito Kodama, Tsutomu Uesugi, Member, IEEE and Hiroshi Tadano, "A Concept of SOI RESURF Lateral Devices with Striped Trench Electrodes", IEEE Transactions on Electron Devices, Vol. 52, No. 6, June 2005 pg. 1205-1210.

- 22) A. Popescu, F. Udrea and W. Milne, "A Numerical study of the RESURF effect in bulk and SOI Power Devices", 1997 IEEE, Department of Engineering, Cambridge University, England.

- 23) Adriaan W. Ludikhuize, "A Review of RESURF Technology", ISPSD' 2000, May 22-25, Toulouse, France.

- 24) A. Popescu, F. Udrea, R. Ng and W.I. Milne, "Analytical modeling for the RESURF effect in JI and SOI power devices", IEEE Proc. - Circuits Devices Syst. VOL. 149, No. 516, October/December 2002.

- 25) S. Merchant, E. Arnold, H. Baumgart, R. Egloff, T. Letavic, S. Mukherjee and H. Plein, "Dependance of Breakdown Voltage on Drift Length and Buried Oxide Thickness in SOI RESURF LDMOS Transistors", 5<sup>th</sup> ISPSD and IC's, 1993 IEEE.

- 26) **Y.S. Huang and B.J. Baliga**, "Extension of RESURF Principle to Dielectrically Isolated Power Devices", 1991 IEEE.

- 27) Ming-Jang LIN, Tsubg-Hwang LEE, Fang-Long CHANG, Chornh-Wei LIAW and Huang-Chung CHENG, "Lateral Super junction Reduced Surface Field Structure for the Optimization of Breakdown and Conduction Characteristics in a High-Voltage Lateral Double Diffused Metal Oxide Field Effect Transistor", Jpn. J. Appl. Phys. VOL 42 (2003), pp. 7227-7231, Part 1, No. 12, December 2003.

- 28) Rene P. Zingg, "New Benchmark for RESURF, SOI and Super junction Power Devices", Proceedings of 2001 International Symposium on Power Semiconductor Devices and IC's, Osaka, 9.43.

- 29) C. Rochefort and R. van Dalen, "Vertical RESURF Diodes Manufactured bt Deep Trench Etch and Vapor-Phase doping", IEEE Electron Devices Letters, Vol. 25, No. 25, No.2, February 2007 pg. 73-75.

- 30) Mueng-Ryul Lee and Oh-Kyong Kwon, "High Performance Extended Drain MOSFETS (EDMOSFETS's) with Metal Field Plate", 1999 IEEE.

- 31) S. Banerjee, K. Chatty, T.P. Chow, R.J. Gutmann, "Improved High Voltage Lateral RESURF MOSFET's in 4H-SiC", IEEE Electron Devices Letters, Vol.22, No.5, May 2001 209-211.

- 32) **P.H. Wilson**, "A Novel HVRF Vertical MOSFET for High Power Applications", 2002 IEEE, Fairchild Semiconductor.

- 33) M. Kittler, F. Schwierz and D. Schipanski, "Scaling of Vertical and Lateral MOSFETS in the Deep Sub micrometer Range", 2000 IEEE.

- 34) Enrico gili, "Fabrication of Vertical MOSFET's with Reduced Parasitics and Suppression of Short Channel Effects", 2004, University of Southampton.

- 35) **G.E.J. Koops, E.A. Hijzen, R.J.E. Heuting, M.A.A. Int Zandt**, "*RESURF* stepped Oxide (RSO) MOSFET for 85V having a Record low Specific On-Resistance", Proceedings of 2004 ISPSD and IC's, Kitakyushu, pg. 185-188.

- 36) M. Zitouni, F. Morancho, P. Rossel, H. Tranduc, J. Bruxo, I. Pages, "A New Concept for the lateral DMOS transistor for Smart Power IC's", LAAS-CNRS, 1999 IEEE.

- 37) **B. Jayant Baliga**, "*An Overview of Smart Power Technology*", IEEE Transactions on Electron Devices, Vol. 38, No. 7, July 1991, pg. 1568-1575.

- 38) Raymond J.E. Hueting, Erwin A. Hijzen, Anco Heringa, Adriaan W. Ludikhuise and Micha A.A. Int Zandt, "Gate Drain Charge Analysis for Switching in Power Trench MOSFET's", IEEE Transactions on Electron Devices, Vol. 51, No.8, August 2004 pg. 1323-1330.

- 39) Qin Lu, P. Ratnam, C. Andre and T. Salama, "*High Voltage SOI MOSFET*'s", 1991 IEEE.

- 40) Dan Tulbure, "Introduction to Power MOSFET's", MicroNote Series 901.

- 41) **Ralph Locher**, "Introduction to Power MOSFET's and their Applications", Application Note 558, October 1998, Fairchild Semiconductor.

- 42) **B. Jayant Baliga**, "*Power Integrated Circuits –A Brief Overview*", IEEE Transactions on Electron Devices, Vol. ED-33, No. 12, December 1986, pg. 1936-1939.

- 43) **Philip L. Hower**, "*Power Semiconductor Devices: An Overview*", Proceedings of the IEEE, Vol. 76, No.4, April 1988.

- 44) Krishna Shenai, "Optimized Trench MOSFET Technologies for Power Devices", IEEE Transactions on Electron Devices, Vol. 39, No. 6, June 1992 pg. 1435-1442.

- 45) **II-Yong Park, Sang-Gi Kim, Jin-Gun Koo and Jongdae Kim**, "*Reduced Cell Pitch and On-Resistance of Trench MOSFET by employing source on Trench sidewall*", Electronics Letters, 18<sup>th</sup> September 2003, Vol. 39, No. 19.

- 46) **MEDICI,** *"Two Dimensional Device Simulation Program"*, version W-2004.09, September 2004, Synopsys Inc.

- 47) **Adolph Blicher**, "Physics of Semiconductor Power Devices", Rep. Prog. Phys. Vol. 45, 1982, The Institute of Physics.

- 48) <u>http://en.wikipedia.org/wiki/Image:PN\_Junction\_Open\_Circuited.png</u>

- 49) http://store.americanmicrosemiconductor.com/diodes.html

## **APPENDIX**

## A.I HYBRID NMOS DEVICE STRUCTURE

Fig. A.I.1 Hybrid NMOS Transistor Schematic.

# A.II SIMULATION DATA

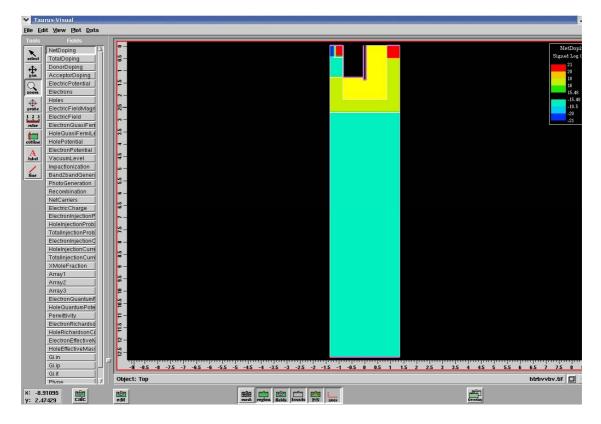

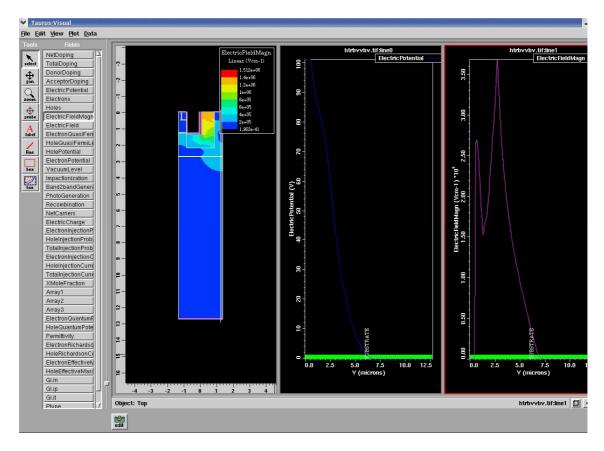

Fig. A.II.2 Taurus Visual 2D- Main Window

Fig. A.II.3 Taurus Visual 2D - Cut Curves Analysis

| Y Probe                                                                                      |                                     |  |  |  |

|----------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|

| X: 1.081 Y: 1.799<br>Region: SUBSTRATE<br>Material: Silicon<br>Fields: Scalar   Magnitude (3 | x,y)                                |  |  |  |

| NetDoping                                                                                    | 4e+16                               |  |  |  |

| TotalDoping                                                                                  | 4e+16                               |  |  |  |

| DonorDoping                                                                                  | 4e+16                               |  |  |  |

| AcceptorDoping                                                                               | 0                                   |  |  |  |

| ElectricPotential                                                                            | 75.51                               |  |  |  |

| Electrons                                                                                    | 0                                   |  |  |  |

| Holes                                                                                        | 0                                   |  |  |  |

| ElectricFieldMagn                                                                            | 2.168e+05                           |  |  |  |

| ElectricField                                                                                | 2.114e+05( -1.211e+05 , 1.733e+05 ) |  |  |  |

| ElectronQuasiFermiLevel                                                                      | 100.5                               |  |  |  |

| HoleQuasiFermiLevel                                                                          | 0                                   |  |  |  |

| HolePotential                                                                                | 76.07                               |  |  |  |

| ElectronPotential                                                                            | 74.95                               |  |  |  |

| VacuumLevel                                                                                  | 70.78                               |  |  |  |

| Impactionization                                                                             | 0                                   |  |  |  |

| Band2bandGeneration                                                                          | 0                                   |  |  |  |

| Photo Generation                                                                             | 0                                   |  |  |  |

| Recombination                                                                                | -6.205e+19                          |  |  |  |

| NetCarriers                                                                                  | 0                                   |  |  |  |

| Electric Charge                                                                              | 4e+16                               |  |  |  |

| ElectronInjectionProbability                                                                 | 0                                   |  |  |  |

| HoleInjectionProbability                                                                     | 0                                   |  |  |  |

| TotalInjectionProbability                                                                    | 0                                   |  |  |  |

| ElectronInjectionCurrent                                                                     | 0                                   |  |  |  |

| HoleInjectionCurrent                                                                         | 0                                   |  |  |  |

| Totalinjection Current                                                                       | 0                                   |  |  |  |

| XMoleFraction                                                                                | 0                                   |  |  |  |

| Array1                                                                                       | 0                                   |  |  |  |

| Anray2                                                                                       | 0                                   |  |  |  |

| Array3                                                                                       | 0                                   |  |  |  |

| ElectronQuantumPotential                                                                     | 0                                   |  |  |  |

| Hole Quantum Potential                                                                       | 0                                   |  |  |  |